**SDP '06**

Matt Brennan mattb@ieee.org 30 March 2006 Note: this will be best viewed in slide-show mode

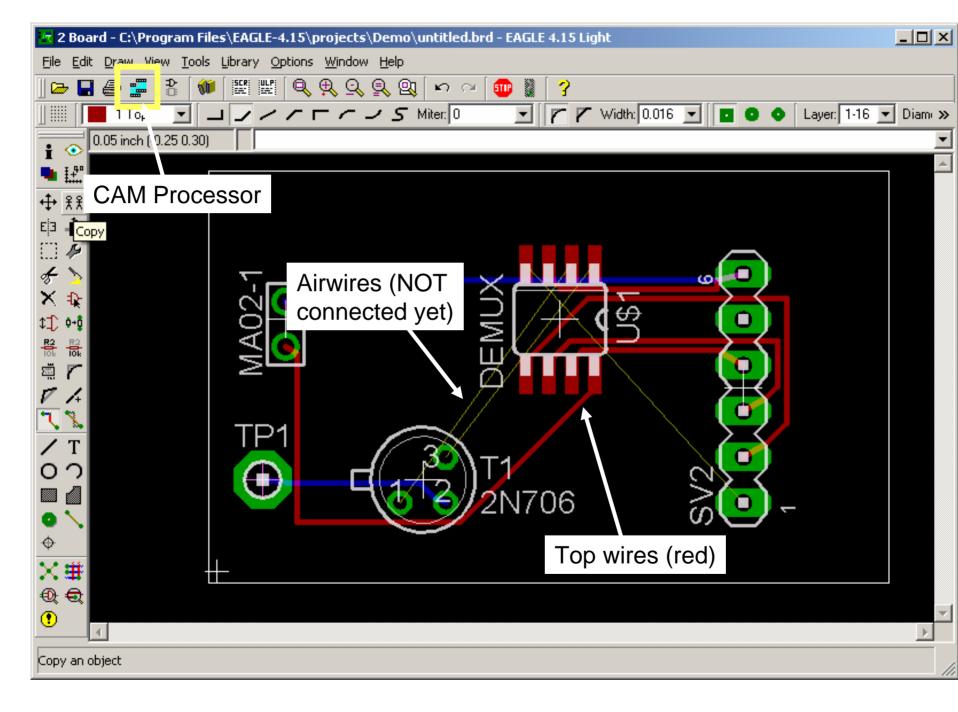

#### **Terms**

- Footprint: what a part looks like on the board

- Airwire: a line in the layout indicating a connection needing to be made

- Silkscreen: notation on PCB (no connection)

- Net: connections between a group of pins

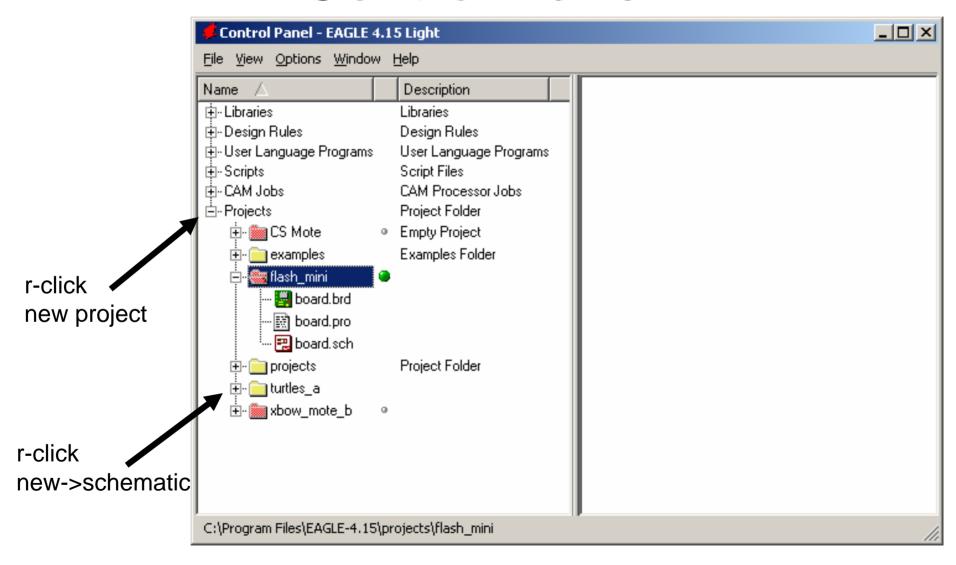

#### **Control Panel**

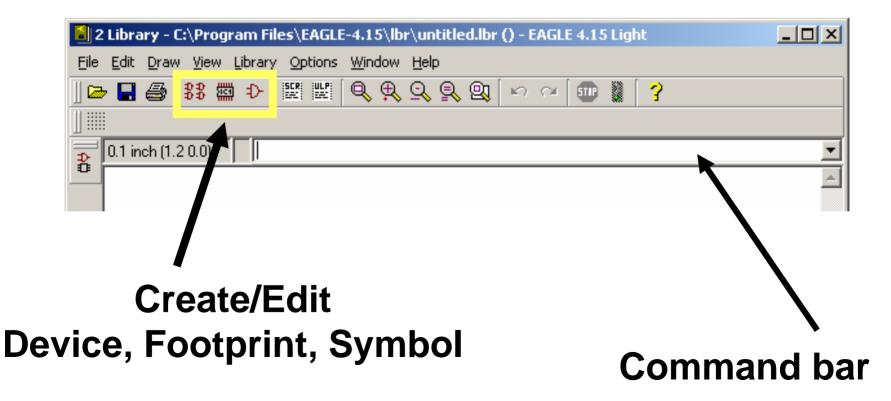

## Making a part

- Symbol + Footprint = Device

- Devices go in to schematic

In command bar: copy so08@40xx so08

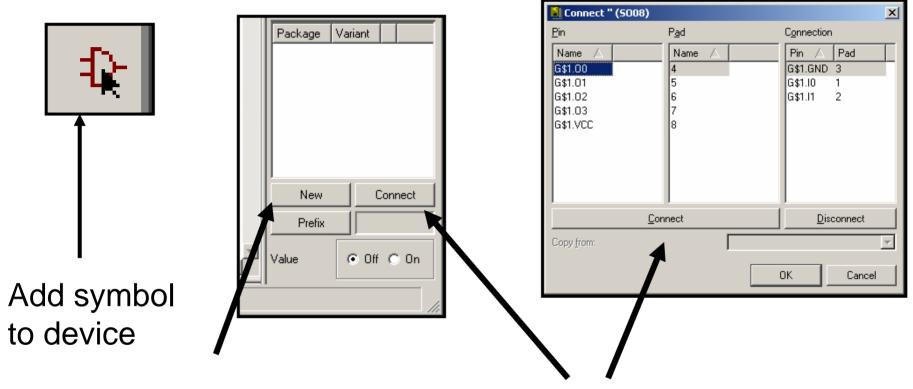

#### Connect device

Make new package, Choose footprint Connect symbol pins to footprint pads

Save library, and "use" it through control panel

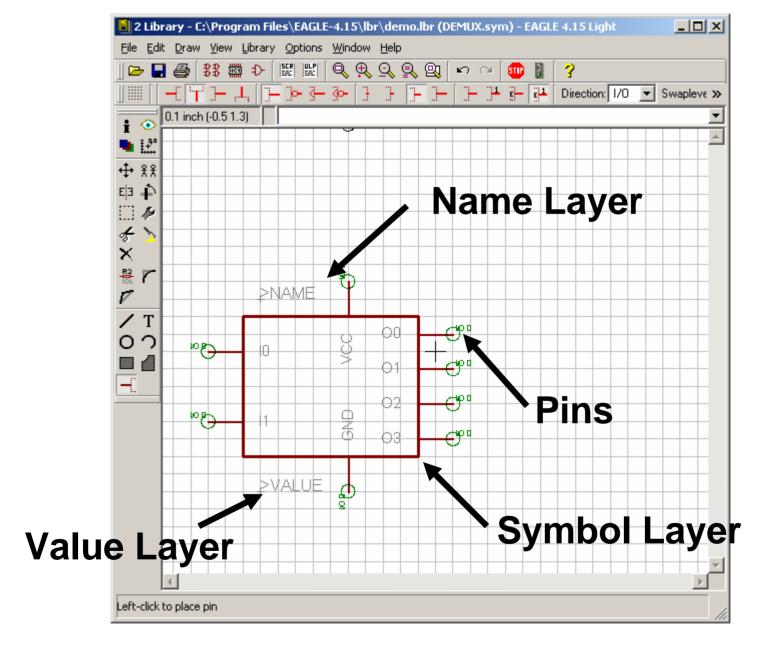

# If you decide to make your own footprint:

- Remember to mark pin1 on something that will be printed

- Put >NAME and >VALUE on the respective layers

- Print the footprint in actual size, line up the part to make sure you got it right

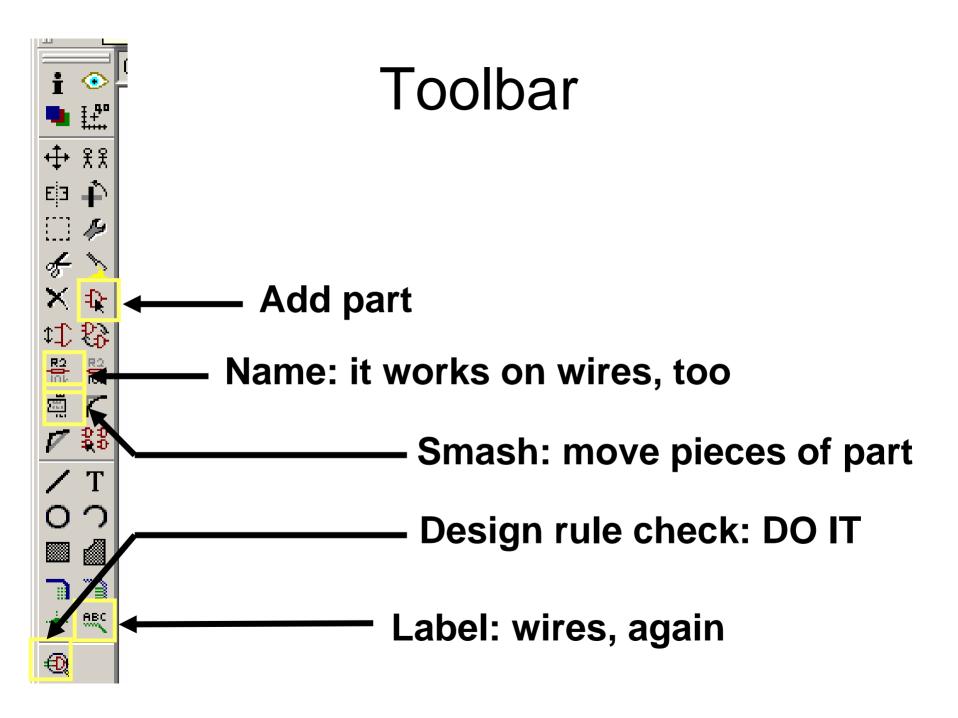

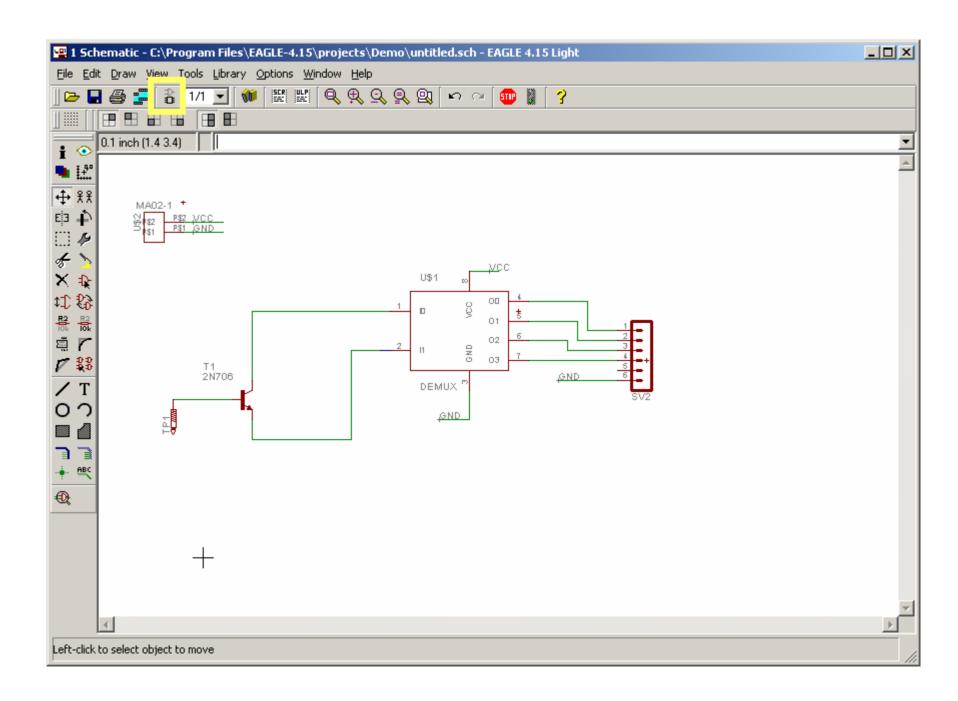

### Schematic Editor

#### Some useful libraries

- rcl resistors, caps, inductors

- con-lstb, con-lsta standard connectors

- con-subd DB-# connectors

- con-coax SMA, etc

- linear op-amps

- solpad extraneous connections

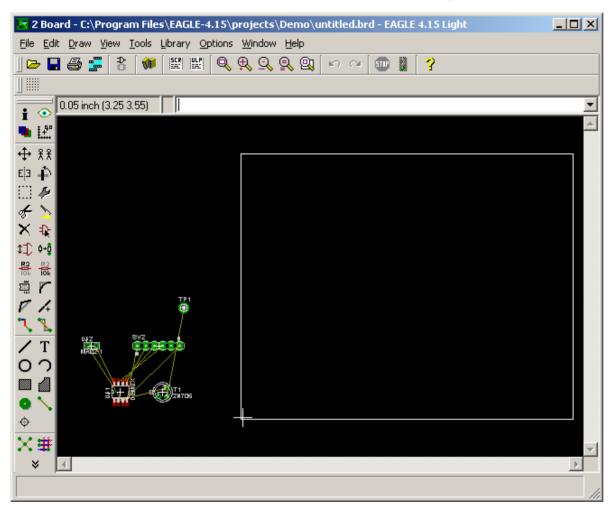

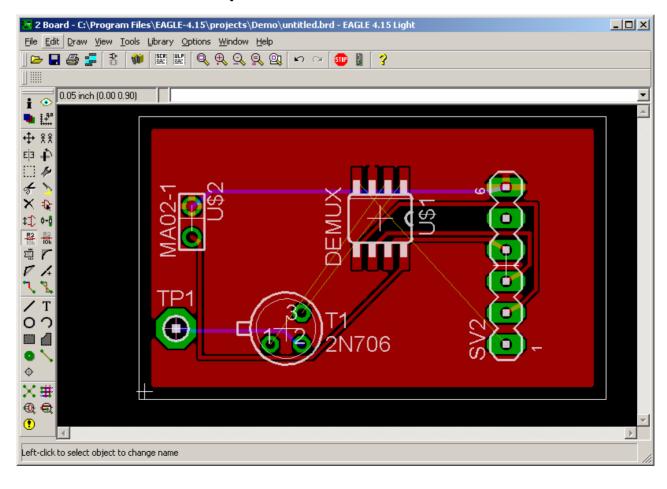

## Layout

- Red: top

- Blue: bottom

- Green: throughhole

- White: dimensions & silk screen

- Can adjust dimensions w/ Move

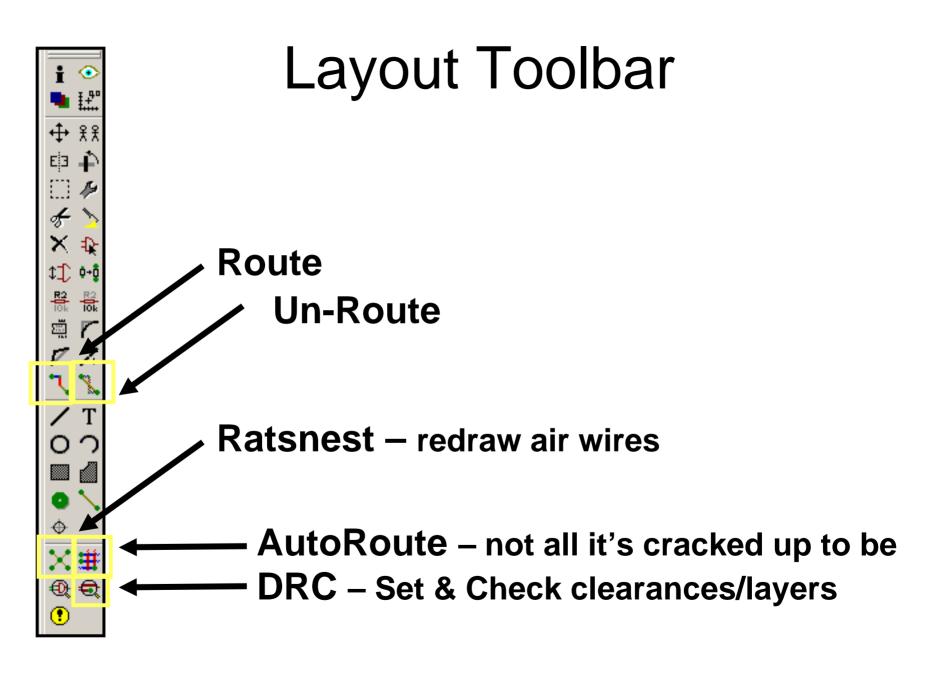

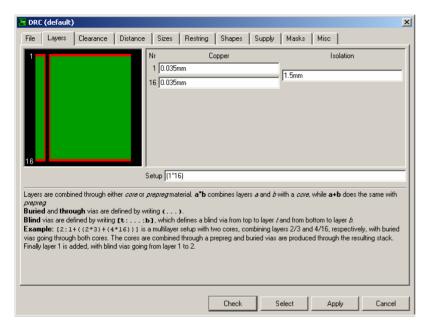

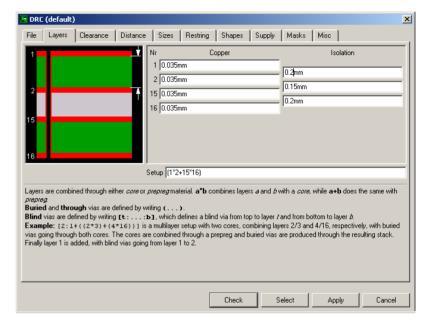

## **DRC** - Layers

Setup: (1\*16) Two Layers Setup: (1\*2+15\*16) Four Layers

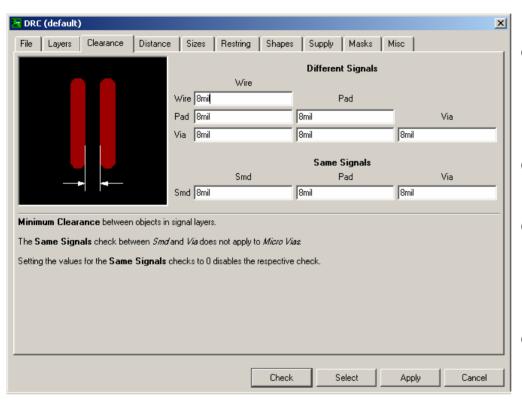

#### DRC - Clearances

- Specified by board house

- Larger => Cheaper

- 6/6 is small, up to 10/10+

- Careful: some SMT packages require small clearances!

Also check: minimum drill size. 12.5 is safe

#### Grid

🔻 Grid

Display.

X

C Lines

Finest

Finest

Cancel

Style

C Dots

inch 🔻

inch 🔻

Last

Normal snap

Size:

Multiple: 1

Alt:

OK

Default

Also set grid in Autoroute options: smaller grid gives router more flexibility, but takes longer to route

## Routing

- High-current traces should be WIDE => less resistance => less voltage drop

- Route power & ground first, "by hand"

- Especially if you are using SMD parts,

READ the layout section of the data sheet

- Anecdotal: DC-DC converters can fry if their passive components are too far away, or traces are too small

# Polygon tool

For large copper areas. Draw polygon, name (with net name), hit 'ratsnest' to fill

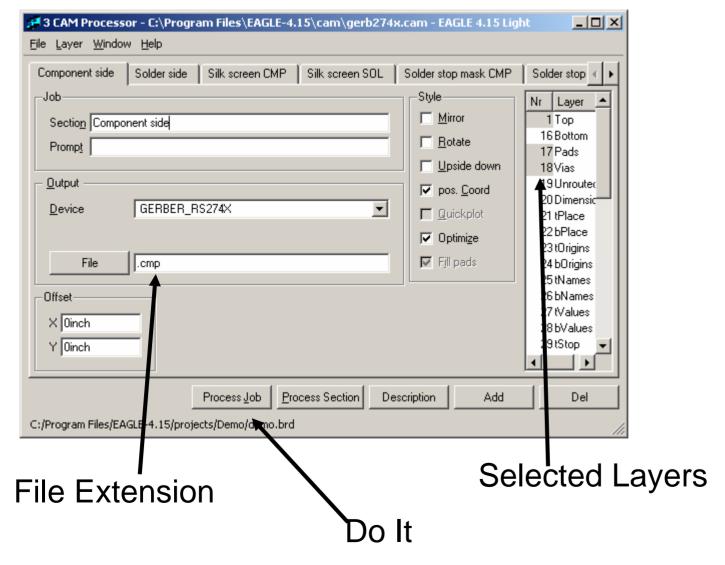

## CAM Processing: Files for board house

# **CAM Processing**

- Two jobs. File->open

- gerb274x (copper data)

- excellon (drill data)

- Add (a) section(s) if doing silkscreen on both sides, or additional layers

- Cheap boards have no silkscreen

- put text on the Top or Bottom copper layers

- make sure there are no accidental connections

#### Other notes

- ALWAYS run ERC & DRC. Then double-check by eye

- Rip all routing?

- Power/GND planes (multiple layers):

- in layout, go to 'layer setup' and name a layer \$GND or \$VCC, or \$netname

- Symbol: Multiple pins with same name?

- VCC\$1, VCC\$2, VCC\$3: anything after \$ won't show in schematic

- Net classes: can define different min sizes for different types of connections (pwr vs data)

- Most commands are available from command bar

- Minimize vias in design

- less resistance, sometimes cheaper boards

- Check status bar for: "Autorouter: 100% finished."

- Otherwise, find what it missed